RISCV Processor Design and Implementation

One of my life dream goals has been to build my own processor from scratch. The advent of Riscv over last couple years has opened up great avenues for one to achieve that, or at least get on the pathway to do so. In this project i work on designing and implementing a basic Riscv 32 bit processor and implemented it on a Spartan 7 FPGA board.

High Level Synthesis Approach

I chose to take the HLS approach as apposed to the traditional HDL approach using VHDL/Verilog. One of the key things that stood out was our quickly i could iterate over my designs, and there seems to be increased in overall intuitiveness of how processors worked when implementing it in a fimiliar programming paradigm such as C++.

About HLS

The High-Level Synthesis (HLS) approach in FPGA IP creation is a revolutionary paradigm that offers a stark contrast to the traditional hardware design flow. In the traditional approach, designers manually specify the low-level hardware description languages (HDLs) like VHDL or Verilog, which can be time-consuming and error-prone. HLS, on the other hand, allows developers to describe the functionality of their hardware IP using high-level languages like C, C++, or SystemC. The HLS tool then automatically transforms this high-level code into optimized hardware implementations, relieving designers from the intricacies of low-level hardware details.

The HLS approach offers several advantages, making it a great choice for accelerated design. First and foremost, it significantly reduces the development time by enabling designers to work at a higher level of abstraction. Writing algorithms and functionality in familiar high-level languages is more intuitive and less error-prone, leading to quicker iterations and shorter time-to-market.

Moreover, HLS facilitates design exploration and optimization. Designers can easily experiment with different algorithms and architectural configurations in software, obtaining performance estimates quickly. This iterative process helps identify the most efficient implementation, which can be challenging to achieve in the traditional HDL-based flow.

Another critical advantage of HLS is the potential for design reuse. High-level code is more portable and can be easily adapted to different FPGA architectures or even migrated to other hardware platforms, which is not always straightforward in the traditional HDL flow.

Overall, the HLS approach empowers designers to focus on algorithmic development and system-level design, promoting a more efficient and accelerated design process. Its abstraction from low-level details simplifies the design flow, reduces development time, and fosters greater innovation, making it a game-changer in FPGA IP creation for accelerated designs.

High Level Architecture

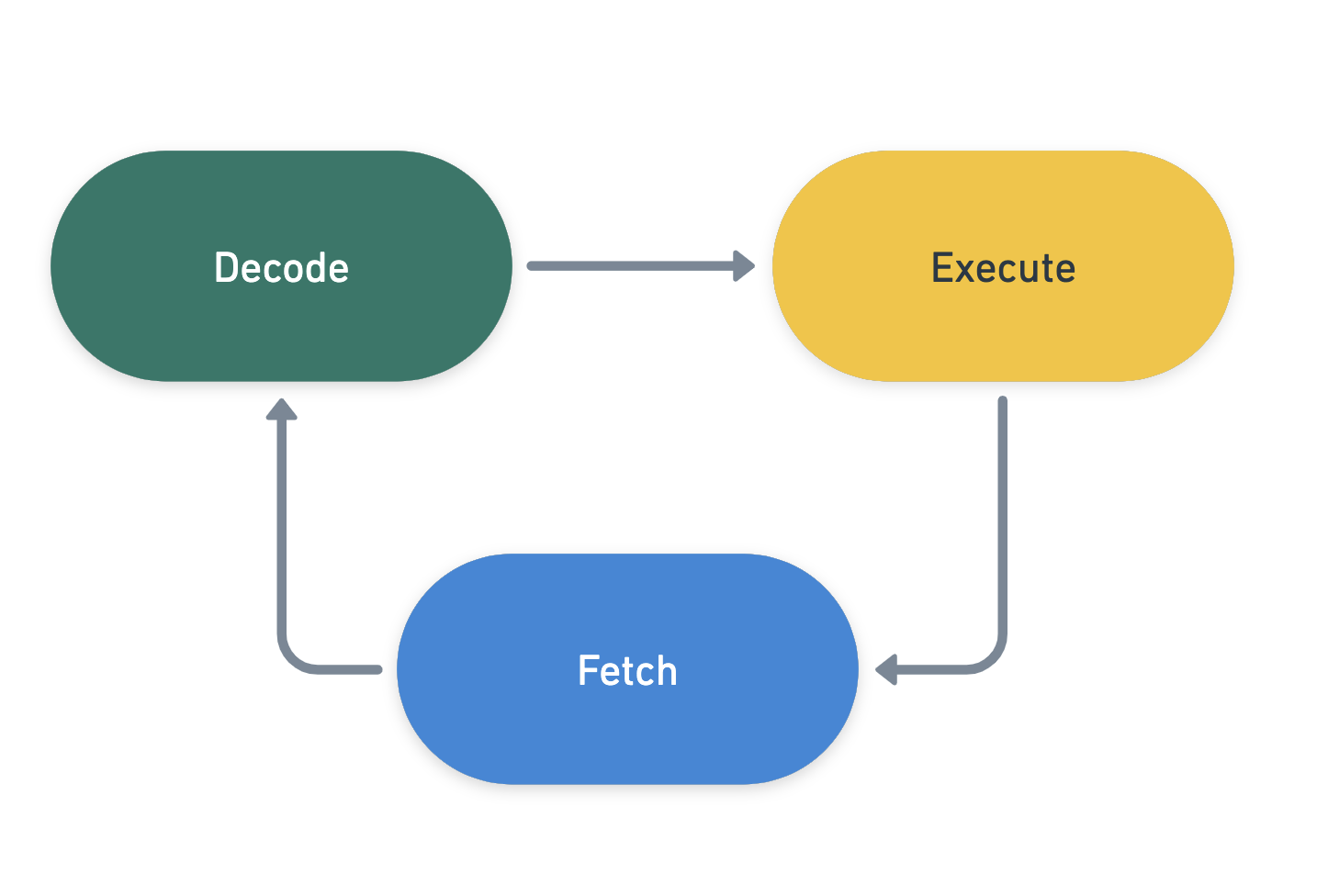

At its most fundamental level a processor does 3 basic things.:

Fetch instructions from memory

Decode Instructions

Execute Instructions

That last execution part will in many cases result in having to also write data into memory. All hardware peripheral control and command can also be reduced to an exercise of write control command to register in memory and reading and responding to status flagged in the associated registers.

The first interesting part was the implementation of the decoder which required a detail understanding the Riscv instruction architecture, its one thing reading the specification and getting a conceptual grasp of things, its a lot more rewarding implementing it and seeing the specifics of how Riscv works. Furthermore seeing it in familiar C++ syntax really cemented all of things.

Secondly the execution part is also very interesting, its here that i became to develop and intuition around how processors actually work, more so where the inefficiencies and optimisations come into play. Its also where one sees the genuis and short comings for the instruction set architecture in how it optimises for making certain operations easier others.

FPGA & Toolchain

From an FPGA perspective i got a hold of the Arty S7 development boarding housing a Xilinx Spartan-7 packing 32k LUTs, which would be more than enough to implement a basic 32bit riscv processor. This in turn meant i could leverage the Xilinx Vivado toolchain which conveniently has a lot of good support for HLS IP design.

ARTY S7, Spartan 7, Vivado

Current implementation

As mentioned above the final System on Chip leverages the Microblaze software which communicates to my Riscv IP over an AxiLite interface. This allows me to develop basic C application which can communicate with my core, and more importantly i can use the Arty s7 uart interface to get feedback on how my core is performing.

Next Steps

My next milestone is to implement a pipelined processor, and explore a more multicore implementation.